#### Lecture #4: Clocking in Synchronous Circuits

Kunle Olukotun Stanford EE183 January 15, 2003

### Tutorial/Verilog Questions?

- Tutorial is done, right?

- Due at midnight (Fri 1/17/03)

- Turn in copies of all verilog, copy of "verification" scripts you wrote, corresponding waveforms annotated, FGPA Editor output (use PrtSc and copy to MS Paint), the part of the implementation output that shows the speed and the amount of logic units utilized.

- Check out the tao of EE183 on the web

# **Course Logistics**

- Labs due every two weeks

- Prelab report due a week before demo

- Demo due on Fridays at **5pm**

- Report due by following Monday at midnight

| Lab | Pre-Lab    | Demo Due | Final      |

|-----|------------|----------|------------|

|     | Report Due | by 5 pm  | Report Due |

| 1   | Jan 17     | Jan 24   | Jan 27     |

| 2   | Jan 30     | Feb 17   | Feb 10     |

| 3   | Feb 14     | Feb 21   | Feb 24     |

| 4   | Feb 28     | Mar 7    | Mar 10     |

• All reports are submitted by email using PDF

#### PreLab

- Encourage you to think about structure of your design before you implement

- Datapath control decomposition

- FSM hierarchy and states

- Better prelab leads to easier implementation

- Worth 2pts of your report

- Demo: 20 pts

- Prelab: 2pts

- Report: 18pts

# Lab 1 Questions?

- VGA

- TCGROM

- Sega Game Controller

- Two dual port memories

- Why?

- 4Kx1 architecture

- CoreGen

### Lab 1: Optional Fun Things

- Display the number of iterations

- Capability to clear the screen

- Instead of the cheesy (but perfectly fine) board reset

- Capability to start with a random game board

- LFSR seeded by counter from powerup

- Fastforward

- Have the next N game states be computed in rapid succession

- Perhaps use a third BRAM

#### Lab 1: Known Interesting Initial States

- Some starting states are more interesting than others

- Have the initialization of the BRAM be one of them.

- Have multiple ones and switch between them

- Use Memutils.zip to generate the BRAMs init files.

- http://groups.yahoo.com/xsboard-users/files

- http://groups.yahoo.com/group/xsboard-users/files/

### Lab 1: Background Image

- When the game state location is off show a background image

- Have another 64x64 BRAM storing the image and index it the same way as the game board. If the location is vacant then display whatever is in the background image.

- we only have 10 4kbit BRAMs

#### Handout #7 Winter 2002/2003

# Lab 1 Design Structure

- Hierarchy of cooperating FSMs

- Master control FSM

- Gamepad FSM

- VGA FSM

- Board update FSM

- Game state FSM

- Datapath elements

- BRAMCounters

- Registers

- Make VGA and gamepad modules resuable

#### Today's Lecture

- Clocking in synchronous systems

- Skew

- jitter

- H clock distribution tree

- Max path, min path, critical path

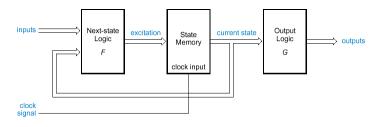

# FSM Timing

- Now that we know how to design a state machine, how fast can we make it run?

- The register-to-register performance is the key metric to consider.

#### Clock Skew

- We have assumed that the clock reaches each DFF simultaneously.

- It should be no surprise that this assumption is not entirely valid.

- Clock Skew is the non-time varying (static) difference in the clock arrival time at two different DFFs.

# Clock Skew

• The wire propagation delay is non trivial and the difference in arrival times for this type of layout is unacceptable.

### H Clock Distribution Tree

- Make Clock distribution tree in the form of an H so that all flops are equidistant to the root of the tree.

- An FPGA is a very regular structure but for an ASIC, there are a variable number of DFFs in each sector.

# Spartan II Skew Data

| XILINX°         | Spartan-II 2.5V F                        | Spartan-II 2.5V FPGA Family: DC and Switching Characterist |       |       |  |  |

|-----------------|------------------------------------------|------------------------------------------------------------|-------|-------|--|--|

| Clock Distribut | ion Guidelines <sup>(1)</sup>            |                                                            |       |       |  |  |

|                 |                                          | Speed                                                      | Grade |       |  |  |

|                 |                                          | -6                                                         | -5    |       |  |  |

| Symbol          | Description                              | Max                                                        | Max   | Units |  |  |

| GCLK Clock Skev | í                                        |                                                            |       |       |  |  |

| TGSKEWIOB       | Global clock skew between IOB flip-flops | 0.13                                                       | 0.14  | ns    |  |  |

Notes: 1. These clock distribution delays are provided for guidance only. They reflect the delays encountered in a typical design under worst-case conditions. Precise values for a particular design are provided by the timing analyzer.

#### Clock Jitter

- Clock Jitter is the time-varying (cycle to cycle) difference in the clock arrival time at the *same* DFF.

- There are many sources of jitter—inaccuracies in the source oscillator, drifting of the Phase Lock Loop (PLL), and crosstalk between the clock and other transitioning signals.

#### Spartan II Jitter Data

#### DLL Clock Tolerance, Jitter, and Phase Information

All DLL output jitter and phase specifications were deter-mined through statistical measurement at the package pins Figure 1, page 13, provides definitions for various parameters in the table below. using a clock mirror configuration and matched drivers.

|                    |                                                                          |           | CLKDLLHF |      | CLKDLL |      |       |

|--------------------|--------------------------------------------------------------------------|-----------|----------|------|--------|------|-------|

| Symbol             | Description                                                              | FCLKIN    | Min      | Max  | Min    | Max  | Units |

| TIPTOL             | Input clock period tolerance                                             |           | -        | 1.0  | -      | 1.0  | ns    |

| TIJITCC            | Input clock jitter tolerance (cycle-to-cycle)                            |           | -        | ±150 | -      | ±300 | ps    |

| T <sub>LOCK</sub>  | Time required for DLL to acquire lock                                    | > 60 MHz  |          | 20   | -      | 20   | μs    |

|                    |                                                                          | 50-60 MHz | -        | -    | -      | 25   | μs    |

|                    |                                                                          | 40-50 MHz | -        | -    | -      | 50   | μs    |

|                    |                                                                          | 30-40 MHz | -        | -    | -      | 90   | μs    |

|                    |                                                                          | 25-30 MHz | -        | -    | -      | 120  | μs    |

| TOJITCC            | Output jitter (cycle-to-cycle) for any DLL clock output <sup>(1)</sup>   |           | -        | ±60  | -      | ±60  | ps    |

| T <sub>PHIO</sub>  | Phase offset between CLKIN and CLKO <sup>(2)</sup>                       |           | -        | ±100 | -      | ±100 | ps    |

| T <sub>PHOO</sub>  | Phase offset between clock outputs on the DLL <sup>(3)</sup>             |           | -        | ±140 | -      | ±140 | ps    |

| T <sub>PHIOM</sub> | Maximum phase difference between CLKIN and CLKO <sup>(4)</sup>           |           | -        | ±160 | -      | ±160 | ps    |

| Трноом             | Maximum phase difference between clock outputs on the DLL <sup>(5)</sup> |           | -        | ±200 | -      | ±200 | ps    |

tes: Output Jitter is cycle-to-cycle jitter measured on the DLL output clock, excluding input clock jitter. Phase Offset between CLKIN and CLKO is the worst-case fixed time difference between rising edges of CLKIN and CLKO, excluding output jitter and input clock jitter. Phase Offset between Clock Outputs on the DLL is the worst-case fixed time difference between rising edges of any two DLL outputs, excluding Output Jitter and input clock jitter. Maximum Phase Difference between CLKIN and CLKO is the sum of Output Jitter and Phase Offset between CLKIN and CLKO, or the greatest difference between CLKIN and CLKO rising edges due to DLL alone (excluding input clock jitter). Maximum Phase Difference between CLKIN and CLKO to LL is the sum of Output Jitter and Phase Offset between any DLL clock outputs, or the greatest difference between any two DLL output rising edges due to DLL alone (excluding input clock jitter). З.

#### **Example Parameters**

• DFF values:

$- T_{clk-p} = 1$ ns,  $T_{setup} = 1$ ns,  $T_{hold} = 1$ ns

- Clock skew is max 2ns and jitter is 2ns

- Combinational logic T<sub>cl\_pdmax</sub>=10ns, T<sub>cl pdmin</sub>=1ns

#### Handout #7 Winter 2002/2003

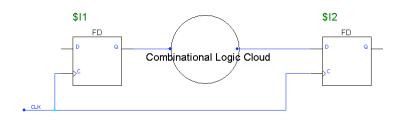

# MaxPath Timing Constraint

- Add up the components that result in the time budget; the period must be greater than this value.

- $T_{clk->q}+T_{cl_pdmax}+T_{setup}+T_{skew}+T_{jitter} \le Clock Period$

- 1 + 10 + 1 + 2 + 2 <= Clock Period

- 16ns <= Clock Period

- Max Frequency is 62.5MHz

### MinPath Timing Constraint

- Consider what happens when the same clock edge is considered at the far DFF.

- $T_{clk->q}+T_{cl_pdmin}>=T_{skew}+T_{jitter}+T_{hold}$

- $1+1 \ge 2+2+1$

- Whoops!! 🛞

- AKA, "Hold-Time Violation"

#### EE183 Olukotun

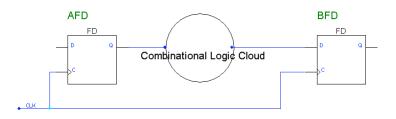

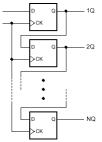

# MinPath and ShiftRegisters

- Shift Registers can easily fall prey to min path timing violations.

- Fix the violations by increasing delay between Ds and Qs

- Insert pairs of inverters

- - $-T_{clk-q} = 1.0$ ns

- $-T_{hold} = 0ns$

- $-T_{skew} = 0.14ns$

- $T_{jitter} = 0.06 ns$

#### Impacts

- You can "fix" MaxPath timing constraint violations by slowing down the clock after the circuit is implemented.

- You *cannot* "fix" MinPath timing constraint violations by modifying the clock.

#### Handout #7 Winter 2002/2003

# Static Timing Tool

- Longest MaxPath Constraint is called *Critical Path* of design.

- Find critical path by calculating all the MaxPath constraints of ever every path in the design and picking the largest.

- Perfect tool for a computer.

- Xilinx Timing Analyzer is an example of a static timing tool.

# Timing Closure Challenges

- When integrate individual blocks that meet timing, the combined system might not meet timing.

- In general have registered outputs from *top-level* blocks.

- This doesn't solve the problem if the chip is so large/fast that a signal cannot propagate all the way across the chip.

- Reason that I/Os are always useful to register

- Not always certain timing budget available on the board.