# Lecture 9: The EE183 Processor

David Black-Schaffer davidbbs@stanford.edu EE183 Spring 2003

### Overview

- Pipelining

- Getting everything right is a very complicated control problem

- Regularize the data path so we can use it more generically

- Encode the control information in the data

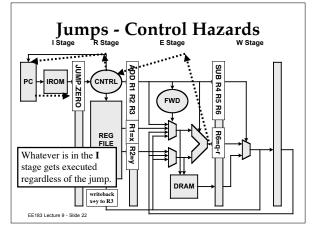

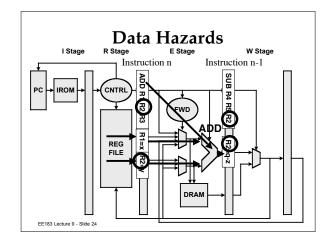

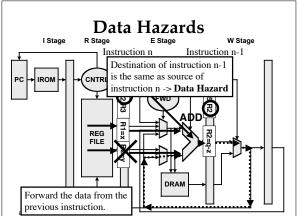

- Hazards

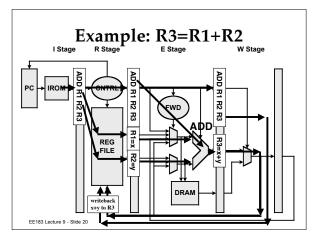

- Watch out for Data and Control Hazards

- Use Forwarding and NOPs in lab 3

EE183 Lecture 9 - Slide 2

# **Public Service Announcement**

- Xilinx Programmable World

- Tuesday, May 6th

- <u>http://www.xilinx.com/events/pw2003/ind</u> <u>ex.htm</u> - free!

- Guest Lectures

- Wednesday, May 7th Gary Spivey on ASIC & FPGA Design for Speed

EE183 Lecture 9 - Slide 3

#### Logistics

- Lab 2 due Friday by 5pm

- Any questions on Lab 2?

# Key points on Pipelining

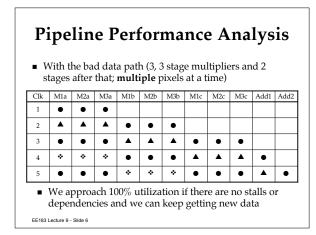

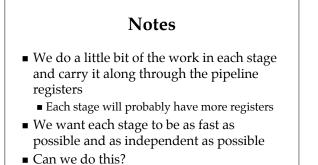

- Increased utilization of functional units only if you can keep the pipeline full

- Keeping the pipeline full requires more complicated control logic

- Data hazards

- Control hazards

```

EE183 Lecture 9 - Slide 7

```

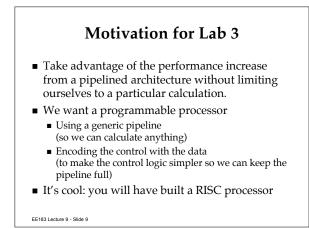

#### Two problems

- Control logic too complicated to keep the pipeline full

- Pipeline specific to one particular problem

- What to do?

- Encode control information with the data

- Use a generic pipeline

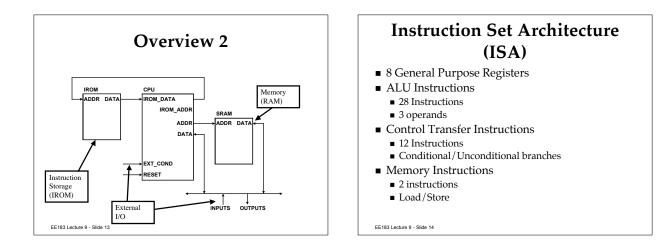

#### What do we want?

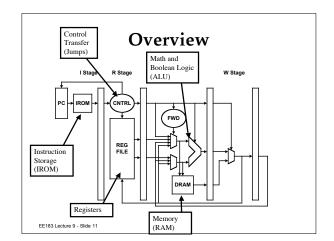

- Obvious stuff:

- Instruction storage

- Math

- Load/Store from/to memory

- Control Transfer (jump if...)

- Less obvious

- Registers (so we don't have to wait for the RAM)

- Boolean Algebra

- External inputs/outputs

- A compiler

- Anything else?

EE183 Lecture 9 - Slide 10

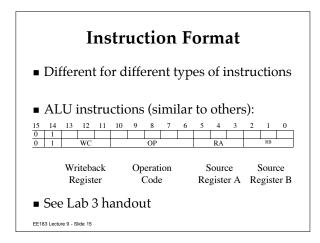

#### **Processor Specs**

- 12-bit RISC MicrocontrollerWhat would having only 8 bits mean for the memory

- architecture? • 8 General Purpose Registers

- 43 Instructions

- 3 operand instructions

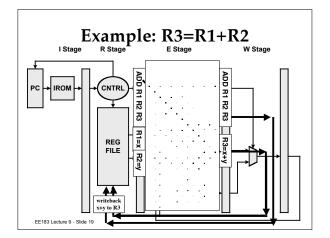

- 4 stage pipeline

- Register indirect addressing mode

- What does this mean?

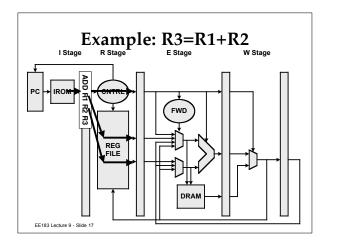

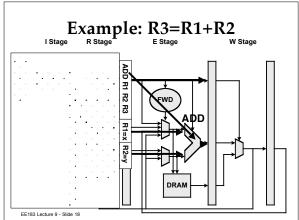

# Instruction Execution Steps 4 Step Sequence Step I Fetch instruction from Instruction Memory Step R Read operands from registers (A, B) Step E Execute instruction, set condition codes Step W Write results to register C So how does this simplify the control logic?

- Not entirely...

- 1100 0110101

EE183 Lecture 9 - Slide 21

EE183 Lecture 9 - Slide 23

# **Control Hazards Solution**

- Insert a NOP after each branch statement (JUMP)

- Now we don't care if the next instruction is executed because it never does anything

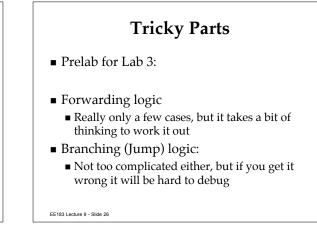

- Template verilog file with some of the pipe registers

- This also has the logic for memory-mapping the DIP switches, but there is a typo

- Register file

- Boolean logic for the ALU

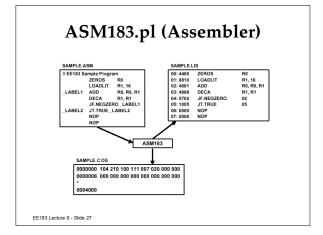

- ASM183 Perl assembler

- Understand the pipeline

- Put together each stage

- Instantiate the RAM & IROM

- Put in the Forwarding

- Add a memory-mapped VGA display

- Add a free-running timer

EE183 Lecture 9 - Slide 29

#### Demo

- Run the three sample programs and display the output on the LEDs/VGA

- Write your own program which uses the free-running counter and the VGA

EE183 Lecture 9 - Slide 30

# Lecture 6 Key Points

- Pipelining only gives you better performance if you can keep the pipeline full

- Regularize the data path and encode the control information with the data to make it easier

- Watch out for Hazards

- Logistics

- Lab 2 demo due Friday by 5pm