# Lecture 10: Memory-mapped I/O and Lab 4

David Black-Schaffer davidbbs@stanford.edu EE183 Spring 2003

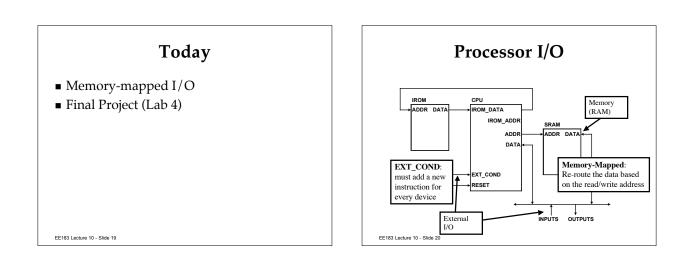

#### Overview

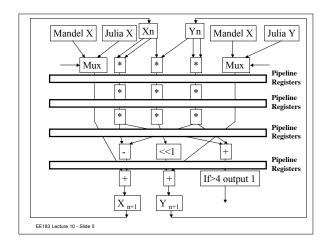

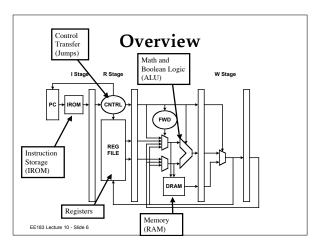

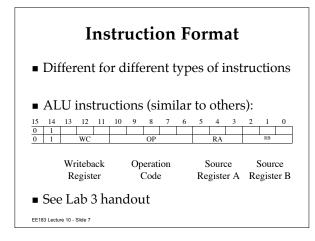

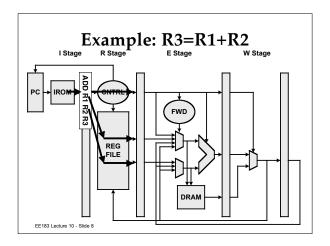

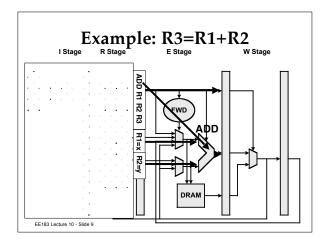

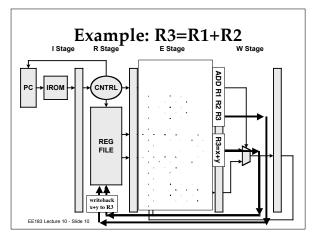

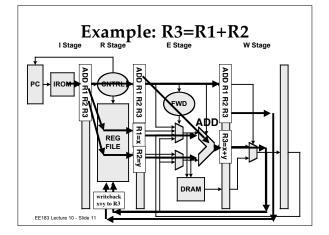

- Pipelining in Lab 3/4

- Do a little bit of work in each stage (fast)

- Keep the control simple by passing it down the pipeline

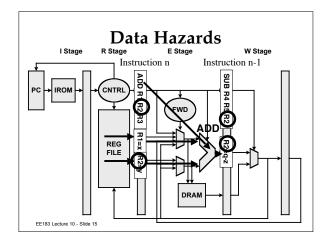

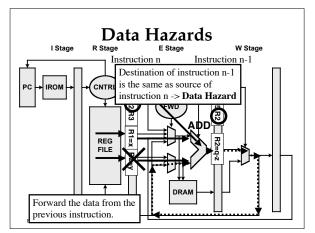

- Deal with Data Hazards through forwarding

- Memory-mapped I/O

- MUX the data lines based on the address

- Use LOAD/STORE to special addresses to transfer data between external devices

EE183 Lecture 10 - Slide 2

## **Public Service Announcement**

- Xilinx Programmable World

- Tomorrow, May 6th

- <u>http://www.xilinx.com/events/pw2003/index.htm</u> free!

- Guest Lecture

- Wednesday, May 7th

- Gary Spivey on ASIC & FPGA Design for Speed

- Also, they are hiring. Info session in Tressider at noon.

EE183 Lecture 10 - Slide 3

#### Logistics

- Lab 2 writeup due tonight by midnight

- Very cool guest lecture tomorrow... (want to break that 200MHz barrier in lab 3?;)

- Next Monday is the last lecture.

## Notes

- Do a little bit of the work in each stage

- Carry it along through the pipeline registers

- We want each stage to be as fast as possible and as independent as possible

- Can we do this?

- Not entirely...

- Prelab for Lab 3:

- Forwarding logic

Really only a few cases, but it takes a bit of thinking to work it out

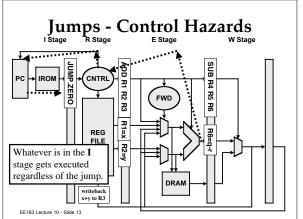

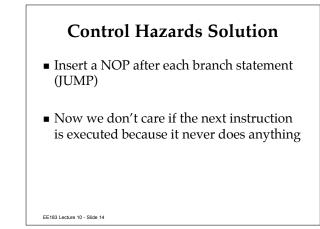

- Branching (Jump) logic:

- Not too complicated either, but if you get it wrong it will be hard to debug

EE183 Lecture 10 - Slide 17

## Lab 3 Requirements

- Implement the processor with forwarding

- Demo the three test programsOutput the result register to the LEDs

- Implement a Timer

- Free-running counter which the processor can use to do things at a specified interval much like the slow clock in Labs 1/2.

- Can be either a new JUMP condition or a memorymapped device

- Implement a memory-mapped VGA display

- Demo a program which uses the VGA and Timer

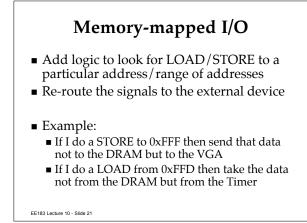

### Implementation

- Simple: look at the RAM address bus and re-route the data and RE/WE signals based on the address (some MUXes)

- Have the external devices respond to these signals to send/receive data

EE183 Lecture 10 - Slide 22

| Usage                                  |                                                                                                   |

|----------------------------------------|---------------------------------------------------------------------------------------------------|

| LOADLIT R1, 0xfff                      | <pre># Define our VGA memory-mapped # address for sending the VGA # {x,y} to the VGA module</pre> |

| ZEROS RO<br># Loop writing to<br>_LOOP | $\#$ Initialize our $\{x,y\}$ to zero the VGA                                                     |

| STORE R1, R0                           | <pre># Write the value of R0 to the VGA # this is our {x,y} location</pre>                        |

| INCA RO, RO<br>JUMP _LOOP              | <pre># Increment the {x,y} location</pre>                                                         |

| <ul> <li>How do we</li> </ul>          | control the color?                                                                                |

| EE183 Lecture 10 - Slide 23            |                                                                                                   |

- Instead of just one VGA location {x,y} address, let's have two:

0xFFF VGA {x,y} {6-bits x,6-bits y}

0xFFE VGA color (4-bits)

- Now the VGA module is more complicated, but we can control the color

|                                            | Usage                                                              |

|--------------------------------------------|--------------------------------------------------------------------|

| LOADLIT R1, Oxfff                          | <pre># Define our VGA memory-mapped # addresss the VGA {x,y}</pre> |

| LOADLIT R2, Oxffe                          | # and the VGA color                                                |

| LOADLIT R3, 0x001                          | # Define a constant for our color                                  |

| ZEROS RO<br># Loop writing to the<br>_LOOP | <pre># Initialize our {x,y} to zero e VGA</pre>                    |

| STORE R1, R0                               | # Write the value of R0 to the VGA<br># this is our {x,y} location |

| STORE R2, R3                               | # Write the color to the VGA                                       |

| INCA RO, RO<br>JUMP _LOOP                  | # Increment the $\{x,y\}$ location                                 |

# Memory-Mapped I/O

- Route the STORE/LOAD data to different places based on the address of the STORE/LOAD

- Bunch of MUXes on the Address/Data lines

- Good way to communicate with many devices (PCI works this way)

- Works better with Tri-stated lines

EE183 Lecture 10 - Slide 26

## Memory-Mapped I/O

Any questions?

## **EE183 Final Project**

- Final Project = Lab 4

- Extend Lab 3 processor to add functionality and increase performance

- 20 additional points on grading for difficulty

- Final demo program

- Two main parts

- Additional Instructions (JAL/JR)

- Something cool...

EE183 Lecture 10 - Slide 28

- Part 1: Add JR (jump register) and JAL (jump-and-link) to the processor

- JAL can have a fixed register to write to, but JR must take an arbitrary register

- Find a good place in the ISA to encode these instructions

- Modify the assembler

- Produce a simple demo program

EE183 Lecture 10 - Slide 29

### EE183 Final Projects (Lab 4)

- Part 2: extend & use the processor

- Three options:

- Accelerate a slow software process in hardware (DES, FIR filters, fractals, cache, graphics, etc.)

- Interface to some external hardware in a cool manner (keyboards, audio, video, etc.)

- Something else cool

- Lab 4 pre-lab due Wed. May 21

- Overview of what you are going to do and how

- Talk to us about how doable your project is first!

EE183 Lecture 10 - Slide 30

## Goals for Lab 4

- Accelerate:

- Quantitatively assess the performance of your implementation

- Performance registers to measure effectiveness

- Compare to other (possible) implementations

- Works very nicely for implementing the fractal lab on the processor

EE183 Lecture 10 - Slide 31

#### Goals for Lab 4

- Interface:

- Better be something pretty cool

- Show how the processor works in the system. (I.e., if it can be better done without a processor then it isn't a good project.)

- Elegant interface to the processor.

- Probably a memory-mapped interface, but make it a smart one.

- Nice for audio filters/keyboard interfaces/graphics

## Goals for Lab 4

- Something else cool:

- Really cool

- If you're excited about it come talk to us and we'll see if it is a good project

- Wide open...

EE183 Lecture 10 - Slide 33

#### Midterm

- Don't forget the midterm a week from this Wednesday.

- 7-9pm in SEQ 102 (next door)

- 45 minute "quiz"

- On the material in the lectures.

EE183 Lecture 10 - Slide 34

## Lecture 6 Key Points

- Pass intermediate results and control info down the pipeline to make it simple

- MUX the RAM data lines based on the address to interface to external devices

- Logistics

- Guest lecture on Speed on Wed.

- **•** Xilinx Programmable World tomorrow

- Last EE183 Lecture ever next Monday